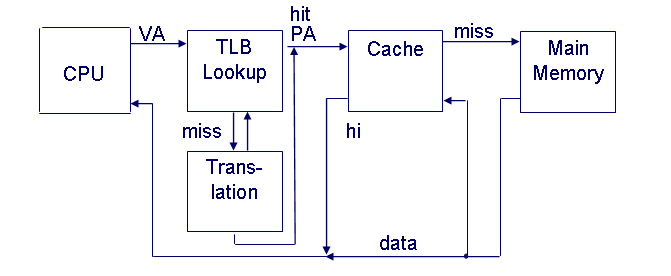

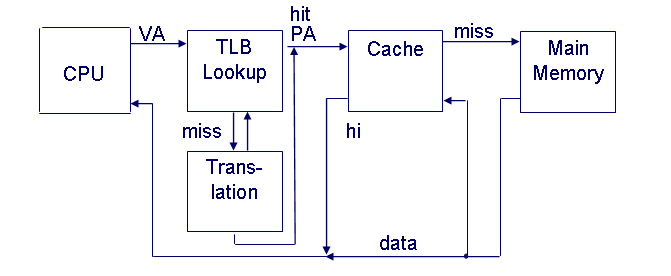

Since the page tables are stored in the main memory, each memory access of a program requires at least one memory accesses to translate virtual into physical address and to try to satisfy it from the cache. On the cache miss, there will be two memory accesses. The key to improving access performance is to rely on locality of references to page table. When a translation for a virtual page is used, it will probably be needed again in the near future because the references to the words on that page have both temporal and spatial locality.

Each virtual memory reference can cause two physical memory accesses :

-One to fetch the page table.

-One to fetch the data.

To overcome this problem a high-speed cache is set up for page table entries called a Translation Lookaside Buffer (TLB).

Translation Lookaside Buffer (TLB) is nothing but a special cache used to keep track of recently used transactions.

TLB contains page table entries that have been most recently used.

Given a virtual address, processor examines the TLB If page table entry is present (TLB hit), the frame number is retrieved and the real address is formed.

If page table entry is not found in the TLB (TLB miss), the page number is used to index the process page table.

TLB first checks if page is already in main memory, if not in main memory a page fault is issued then the TLB is updated to include the new page entry.